VHDL交通灯控制

一、项目目的

设计十字路口交通灯控制电路。通过本次实验,要求能够将已有的实体文件

转换为图形符号,并通过图形输入方式实现电路的连接并设定图形电路层的接口;

深入理解结构描述方法和图形输入法的关系。

二、需准备条件

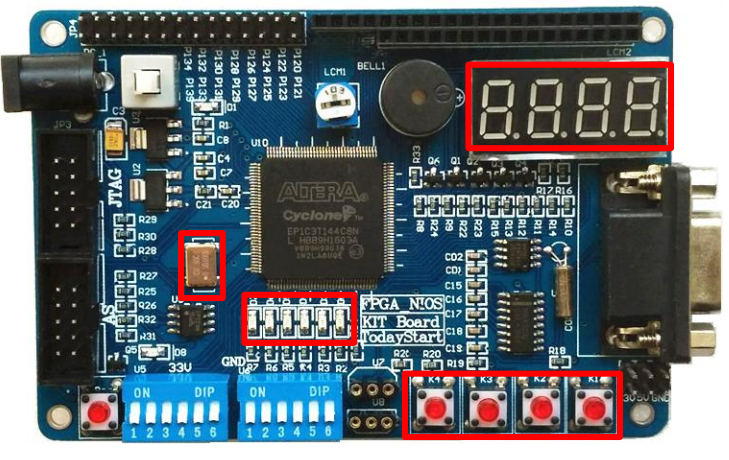

(1) Windows7 或更高版本的操作系统的 PC 机;

(2)安装 QuartusII9.0 EDA 软件;

(3)Cyclone 系列 EP1C3T144 开发板。

三、项目原理

通过 VHDL 编程,实现交通灯控制电路“TrafficLight”。

(1)端口要求:

clk:50MHz 时钟输入;

reset:异步复位信号,低电平有效;

led_h[2..0]:h 方向的三色灯输出;

led_v[2..0]:v 方向的三色灯输出;

seg8_addr[3..0]:四位数码管的使能信号线,低电平有效;

seg8_data[7..0]:四位数码管的数据总线,低电平有效;

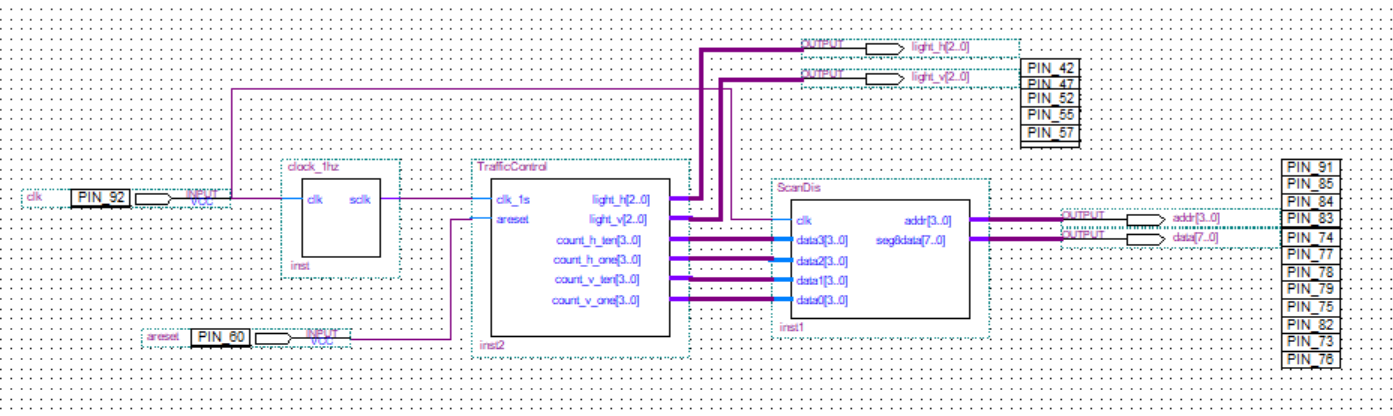

撰写三个独立的实体文件,分别为“Clock_1Hz.vhd”、 “TrafficControl.vhd”和“ScanDis.vhd”,并生成对应的图形符号。在图形输入界面将图形符号实例化后连接构成顶层电路图。

(2)功能要求:

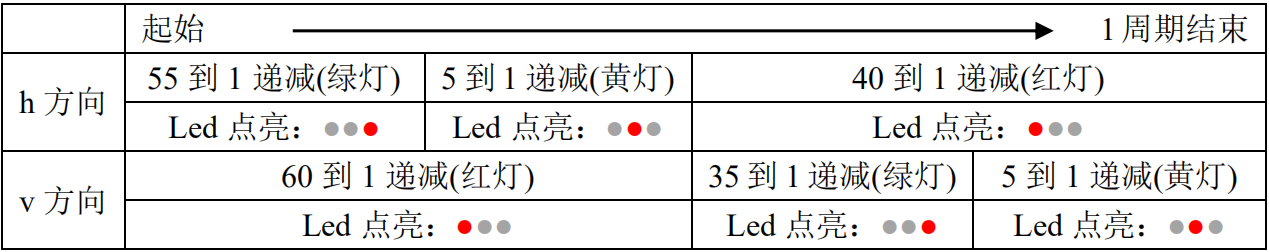

设十字路口为 h(东西)方向和 v(南北)方向,h 方向为主干道,绿灯时间稍长。要求整个控制周期为100秒,系统复位后h方向为绿灯(计数显示55秒), v 方向为红灯(计数显示 60 秒),其控制具体要求如下表所示:

TrafficControl 模块是本设计的核心模块,要求输入端包括秒脉冲和异 步复位信号;输出为两组三色灯信号和计数器值信号。注意,计数值输出为 4 位二进制数,每个方向分为个位和十位两组,所以要求在设计中将计数结果的个 位和十位分别取出。比如当前计数为 37,则需要通过数学计算分别取出数值“3” 和“7”,然后通过接口送出到显示模块 ScanDis。

四、外围电路原理

本次实验所用的外围电路包括时钟电路、独立按键电路、6 位 Led 显示电路

和数码管显示电路,其电路原理图和实物图如下图所示。

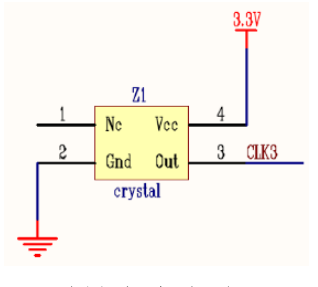

图 3:时钟产生电路-50MHz

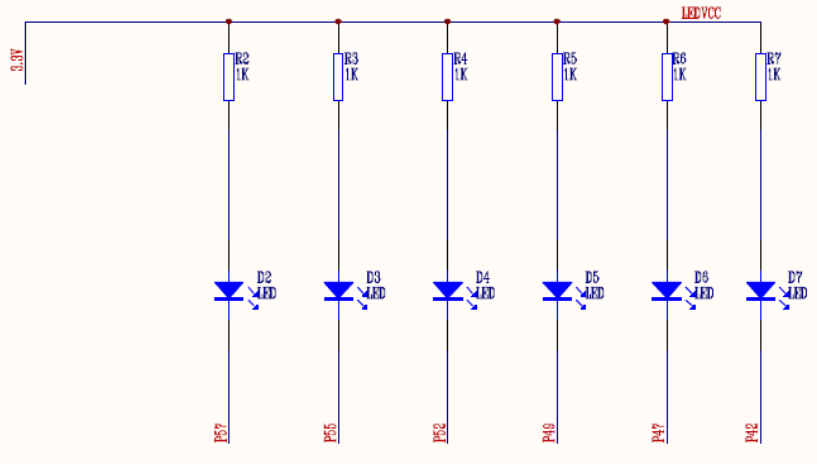

图 4:6 位 Led 显示电路

图 5:4 位独立按键电路

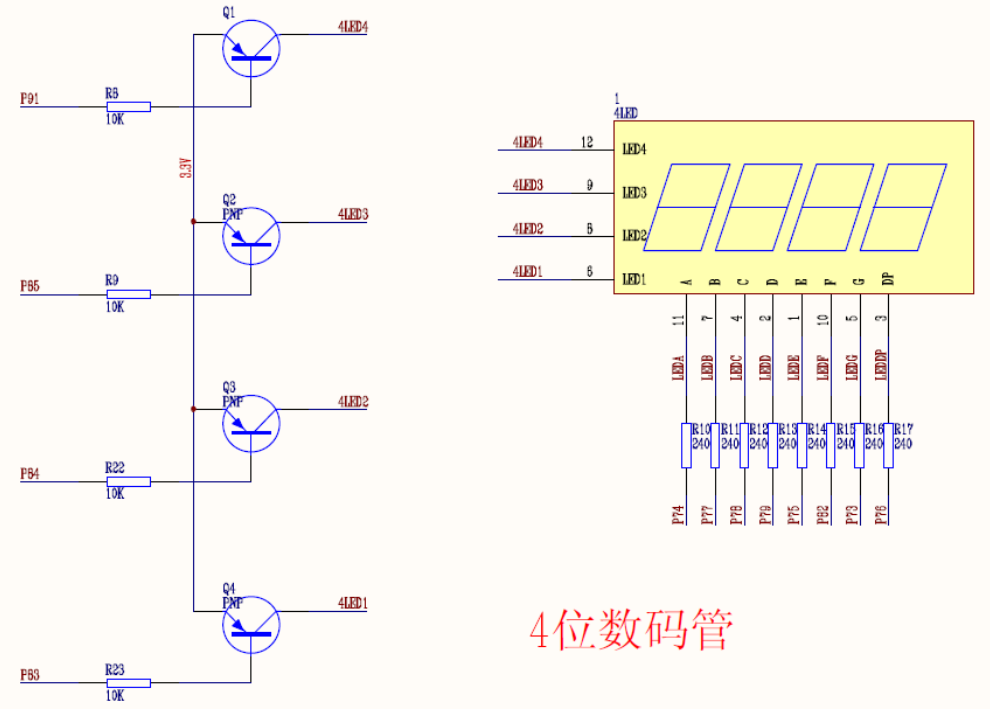

图 6:4 位数码管显示电路

图 7:硬件实物

6位Led发光发光管请选择左边3位为h方向三色灯;右边3位为v方向三色灯;数码管左边两位显示 h 方向计数值,右边两位显示 v 方向技术值;系统复位按键可任意从独立按键中选择。

四、主要代码

1、clock_1hz

entity clock_1hz is

port(clk:in std_logic;

sclk:out std_logic);

end entity clock_1hz;

architecture one of clock_1hz is

signal temp:std_logic;

signal counter:integer range 0 to 50000000:=0;

begin

process(clk)

begin

IF (clk'event AND clk='1') THEN

if(counter=25000000)then

temp<=not temp;

counter<=0;

else

counter<=counter+1;

end if;

end if;

end process;

sclk<=temp;

end architecture one;

2、ScanDis

entity ScanDis is --将数码管扫描显示功能做成块语句

port(clk:in std_logic; --开发板时钟源 50MHz

data3:in integer range 0 to 15;--千位数码管接口输入信号,4 位二进制数

data2:in integer range 0 to 15;--百位数码管接口输入信号,4 位二进制数

data1:in integer range 0 to 15;--十位数码管接口输入信号,4 位二进制数

data0:in integer range 0 to 15;--个位数码管接口输入信号,4 位二进制数

addr:out std_logic_vector(3 downto 0); --4 位数码管使能信号(地址信号)

seg8data:out std_logic_vector(7 downto 0));--4 位数码管公共数据信号

end entity ScanDis;

architecture one of ScanDis is

begin

process(clk)

constant MAX_DIV:integer:=25000;

variable counter:integer range 0 to MAX_DIV;

variable addr_counter:integer range 0 to 3; --地址计数器

variable data_temp:integer range 0 to 15;

begin

if(clk'event and clk='1')then

if(counter=MAX_DIV-1)then

counter:=0;

addr_counter:=addr_counter+1; --地址循环计数 0~3

case addr_counter is

--输出对应的地址使能信号并读取对应位置的数值到 data_temp

when 0=>addr<="0111";data_temp:=data3;

when 1=>addr<="1011";data_temp:=data2;

when 2=>addr<="1101";data_temp:=data1;

when 3=>addr<="1110";data_temp:=data0;

end case;

case data_temp is

--根据数值选择输出数码形状信号

when 0=>seg8data<="00000011";

when 1=>seg8data<="10011111";

when 2=>seg8data<="00100101";

when 3=>seg8data<="00001101";

when 4=>seg8data<="10011001";

when 5=>seg8data<="01001001";

when 6=>seg8data<="01000001";

when 7=>seg8data<="00011111";

when 8=>seg8data<="00000001";

when 9=>seg8data<="00001001";

when 10=>seg8data<="11111101";

when 11=>seg8data<="11111111";

when 12=>seg8data<="11111111";

when 13=>seg8data<="11111111";

when 14=>seg8data<="11111111";

when 15=>seg8data<="11111111";

end case;

else

counter:=counter+1;

end if;

end if;

end process;

end architecture one;

3、TrafficControl

此处注意a1_2, a2_3, a3_4, a4_1为四个标志位,上升沿时表示状态切换,四个标志位代表四个切换节点。

entity TrafficControl is

port(clk_1s:in std_logic;

areset:in std_logic;--此为复位信号

light_h:out std_logic_vector(2 downto 0);

light_v:out std_logic_vector(2 downto 0);

count_h_ten:out integer range 0 to 15;

count_h_one:out integer range 0 to 15;

count_v_ten:out integer range 0 to 15;

count_v_one:out integer range 0 to 15);

end entity TrafficControl;

architecture one of TrafficControl is

signal counter_h:integer range 0 to 100;

signal counter_v:integer range 0 to 100;

signal a1_2,a2_3,a3_4,a4_1:std_logic:='0';

begin

process(clk_1s)

begin

if(clk_1s'event and clk_1s='1')then

count_h_ten<=counter_h/10;

count_h_one<=counter_h rem 10;

count_v_ten<=counter_v/10;

count_v_one<=counter_v rem 10;

end if;

end process;

process(clk_1s,areset)

begin

if(areset='0')then

a4_1<='1';counter_h<=55;counter_v<=60;

else

if(clk_1s'event and clk_1s='1')then

if(a4_1='1')then

counter_v<=counter_v-1;

if(counter_h>=1)then

counter_h<=counter_h-1;

elsif(counter_h<1)then

a4_1<='0';a1_2<='1';

counter_h<=5;

end if;

elsif(a1_2='1')then

counter_v<=counter_v-1;

if(counter_h>=1)then

counter_h<=counter_h-1;

elsif(counter_h<1)then

a1_2<='0';a2_3<='1';

counter_h<=40;

counter_v<=35;

end if;

elsif(a2_3='1')then

counter_v<=counter_v-1;

if(counter_h>=6)then

counter_h<=counter_h-1;

elsif(counter_h<6)then

a2_3<='0';a3_4<='1';

counter_v<=5;

end if;

elsif(a3_4='1')then

counter_v<=counter_v-1;

if(counter_h>=1)then

counter_h<=counter_h-1;

elsif(counter_h<1)then

a3_4<='0';a4_1<='1';

counter_h<=55;

counter_v<=60;

end if;

else

counter_h<=88;

counter_v<=88;

end if;

end if;

end if;

end process;

process(clk_1s)

begin

if(a1_2='1')then

light_h<="101";light_v<="011";

elsif(a2_3='1')then

light_h<="011";light_v<="110";

elsif(a3_4='1')then

light_h<="011";light_v<="101";

elsif(a4_1='1')then

light_h<="110";light_v<="011";

end if;

end process;

end architecture;

五、模块信号端口连接示意

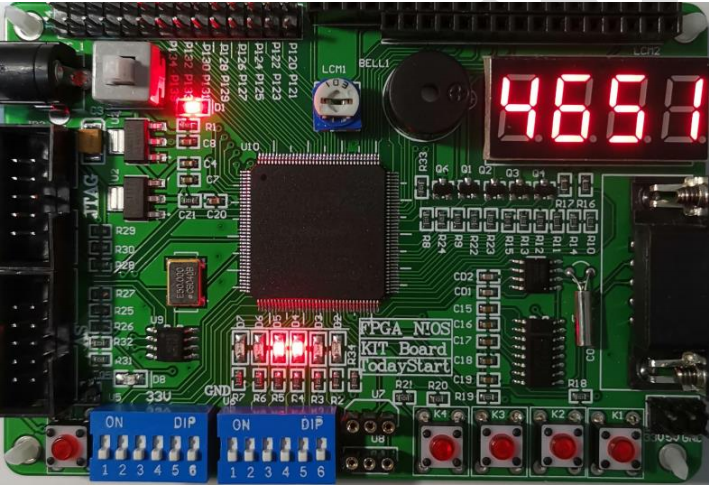

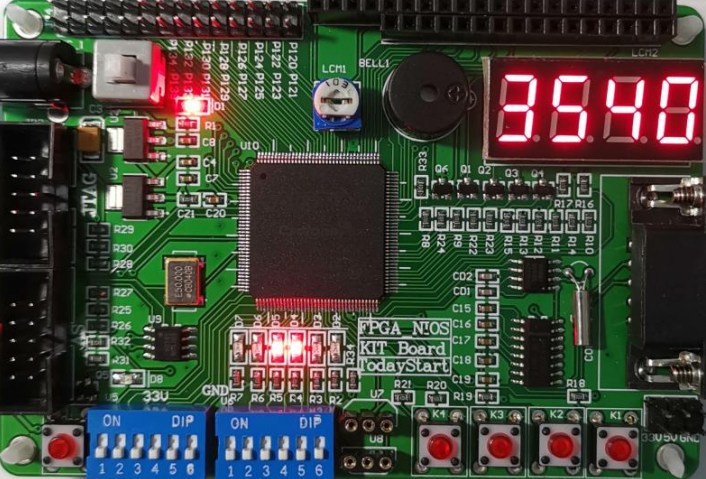

六、运行结果

h方向绿灯通行,剩余46秒;v方向红灯禁行,剩余51秒

h方向绿灯通行,剩余35秒;v方向红灯禁行,剩余40秒

七、提示

本文仅供学习交流,本项目有助于FPGA入门。FPGA具有开发周期短、灵活性强的优势。近些年来应用领域已由通信逐渐拓展至各行各业(就业前景一片光明_~_)。因此,强烈不推荐直接将源代码粘贴复制,甚至直接将文中图片下载交差了事。